High-speed data converters

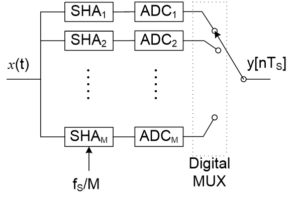

在特定製程下,單一通道類比數位轉換器的操作速度具有一定的限制,分時多工(Time-interleaving)架構常常被用於突破此限制,透過並行多個通道提高轉換器的整體操作速度。然而分時多工電路系統中,每個通道的電路可能存在相互不匹配,例如取樣放大器 (SHA)具有有限的帶寬,並且每個SHA的頻寬可能都不相同,將來各自通道的數位碼併在一起時將造成非線性失真。在這個作品中,我們提出了一種基於數位訊號處理的背景式校正技術,補償此類不匹配造成的誤差,改善高速類比數位轉換器的解析度。

Tsung-Heng Tsai, P. J. Hurst, and S. H. Lewis, “Bandwidth mismatch and its correction in time-interleaved analog-to-digital converters,” IEEE Transactions on Circuits and Systems-II, vol. 53, no. 10, pp. 1133-1137, Oct. 2006.